# Sirindhorn International Institute of Technology

# Thammasat University at Rangsit

School of Information, Computer and Communication Technology

# ECS371: Sample Problems for Midterm Examination

| COURSE                                    | : ECS371 (Digital Circuits) |  |  |

|-------------------------------------------|-----------------------------|--|--|

| DATE                                      | : July 30, 2009             |  |  |

| SEMESTER                                  | : 1/2009                    |  |  |

| <b>INSTRUCTOR</b> : Dr. Prapun Suksompong |                             |  |  |

| TIME                                      | : 13:30-16:30               |  |  |

| PLACE                                     | : BKD 3207 and BKD 3216     |  |  |

| Name    | ID   |  |

|---------|------|--|

| Section | Seat |  |

### **Instructions:**

- 1. Including this cover page, this sample exam has 8 pages.

- 2. Read the questions carefully.

- 3. Write your **first name and ID** on each page of your examination paper.

- 4. Write all your work in the space provided. You may not get full credit even when your answer is right without all of your work written down.

- 5. Closed book. Closed notes. No calculator.

- 6. Allocate your time wisely.

- 7. Do not cheat. The use of communication devices including mobile phones is prohibited in the examination room.

- 8. Your scores will depend strongly on the clarity and completeness of your solutions.

- 9. Do not panic.

# Note: The actual exam will (most likely) be shorter.

## Part A: TRUE/FALSE.

Write 'T' if the statement is true and 'F' if the statement is false. If the statement is false, explain why. Put your answers/explanations in the table given below.

- 1. When the inputs to a 2-input AND gate are both LOW, the output is LOW.

- 2.

- 3.

| Question | T/F | Explanation |

|----------|-----|-------------|

| 1        |     |             |

| 2        |     |             |

| 3        |     |             |

## Part B: MULTIPLE CHOICE.

Choose the one alternative that best completes the statement or answers the question. Put your answers in the table given below.

- 4. A multiplexer with four select, or address, lines can select one of \_\_\_\_\_\_ inputs.

- a. 7

- b. 3

- c. 15

- d. 16

- 5.

- 6.

| Question | Answer |

|----------|--------|

| 4        |        |

| 5        |        |

| 6        |        |

## Part C

- 7. Convert the following binary numbers to decimal:

- a. 10000

- b. 10001

- c. 10101

- 8. What is the largest decimal number that can be represented in binary with 8 bits?

- 9. How many bits are required to represent the following decimal numbers?

- a. 100

- b. 300

- c. 600

- 10. Determine the weight of the 5 in the following decimal numbers:

- a. 12345

- b. 54321

- c. 23541

11. Convert each decimal number to binary using repeated division by 2:

- a. 40

- b. 100

- 12. Determine the 2's complement of the following binary numbers

- a. 0001

- b. 1000

- c. 11001

13. Express each decimal number as an 8-bit number in the 2's complement form:

- a. +20

- b. -33

14. Determine the decimal value of each signed binary number in the 2's complement form:

- a. 11000000

- b. 00011101

- 15. Describe the sign extension process for 2's complement signed numbers. Then, give two examples.

- 16. For 7 bits 2's complement signed numbers, the range is \_\_\_\_\_\_ to \_\_\_\_\_

- 17. Give at least two MAIN advantages of using 2's complement signed numbers.

- 18. Using Boolean algebra, simplify the following expressions into a minimal sum:

a.

$$X = AB + \overline{A}C + BC + A\overline{B}C$$

- 19. Represent the number "-9" using eight bits in each of the representation below:

- a. "-9" in sign-magnitude representation: \_\_\_\_

- b. "-9" in 1's complement representation: \_\_\_\_\_

- c. "-9" in 2's complement representation:

- 20. Construct a 4-input AND gate using 2-input AND gates. (Other gates can not be used!) You may use at most three 2-input AND gates.

- 21. Construct a 4-input NAND gate using 2-input NAND gate. (Other gates can not be used!) You may use at most five 2-input NAND gates.

- 22. Develop a truth table for each of the following expressions.

- a. X = A + BC + CD

#### b.

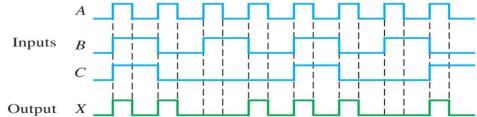

23. For the input waveforms in the figure below, what logic circuit will generate the output waveform shown?

- a. Determine the canonical sum representation of the circuit.

- b. Implement the circuit using AND-OR configuration.

- c. Implement the circuit using NAND gates.

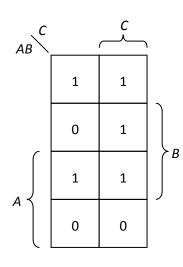

24. Find ALL prime implicants in the following Karnaugh maps.

a.

b.

- 25. Use a Karnaugh map to reduce each expression to a minimum SOP form. For each term in your minimum SOP expression, indicate clearly which group on the K-map corresponds to that term.

- a.  $A \cdot \overline{C} \cdot \overline{D} + A \cdot B \cdot \overline{C} + A \cdot \overline{B} \cdot D + \overline{A} \cdot \overline{B} \cdot \overline{C} \cdot D + A \cdot B \cdot C \cdot \overline{D}$ b.

- 26. Let  $X = AB + \overline{A}C + BC$

- a. Develop a truth table for X

- b. Determine the canonical sum that represents *X*.

- c. Determine the minterm list that represents *X*.

- d. Determine the maxterm list that represents X.

- e. Determine the canonical product that represents X.

- f. Determine the K-map that represents X.

- g. Find ALL the prime implicants in the K-map.

- h. Determine the minimal sum for *X*. For each term in your minimal sum, indicate clearly which group on the K-map corresponds to that term.

- i. Using Boolean algebra, simplify AB + AC + BC into the minimal sum that you got in the previous question.

- j. Implement the minimal sum using AND-OR circuit.

- k. Implement the minimal sum using NAND gates.

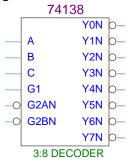

- I. Implement the minimal sum using one 3:8 decoder and one OR gate.

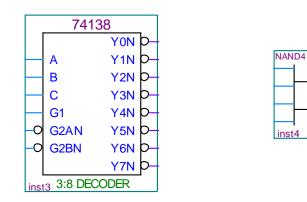

- m. Implement the minimal sum using one 74x138 and one NAND gate.

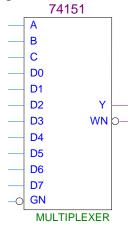

- n. Implement the minimal sum using one 8:1 MUX.

- o. Implement the minimal sum using one 74x151.

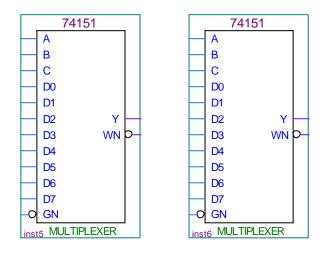

27. In class, we implemented a full-adder using a 3:8 decoder and two OR gates. For this question, implement a full-adder using two 74x151s.

28. Implement the logic function specified in the table below by using only a 74x138 and a NAND gate.

| Input |   |   | Output |

|-------|---|---|--------|

| Х     | Y | Ζ | W      |

| 0     | 0 | 0 | 0      |

| 0     | 0 | 1 | 1      |

| 0     | 1 | 0 | 0      |

| 0     | 1 | 1 | 0      |

| 1     | 0 | 0 | 1      |

| 1     | 0 | 1 | 1      |

| 1     | 1 | 0 | 1      |

| 1     | 1 | 1 | 0      |

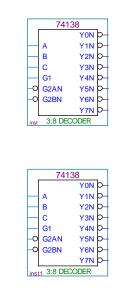

Your score depends strongly on your explanation of your answer. Zero score may be given even for a correct answer if the explanation is incomplete.

29. Construct a 4:16 decoder with an active-HIGH enable (EN) and active-LOW outputs from two 74x138 decoders and one NOT gate. Label the inputs of the 4:16 decoder by I<sub>3</sub>, I<sub>2</sub>, I<sub>1</sub>, I<sub>0</sub> where I<sub>3</sub> is the MSB. Label the outputs of the 4:16 decoder by O<sub>15</sub>\_L, O<sub>14</sub>\_L, O<sub>13</sub>\_L, O<sub>12</sub>\_L, ..., O<sub>1</sub>\_L, O<sub>0</sub>\_L.

$\searrow$

Again, your score depends strongly on your explanation of your answer. Zero score may be given even for a correct answer if the explanation is incomplete.